Technology

Standard Logic based Embedded Flash Memory

We provide a logic compatible embedded flash (Logic EFlash) memory that does not require any process overhead beyond standard CMOS process. This is a cost-effective and secure embedded Non-Volatile Memory (eNVM) IP suitable for your System-on-Chip (SoC). Our proprietary IPs include reliable standard logic based NVM cell and high voltage circuits without requiring any process modification of the generic foundry process technology.

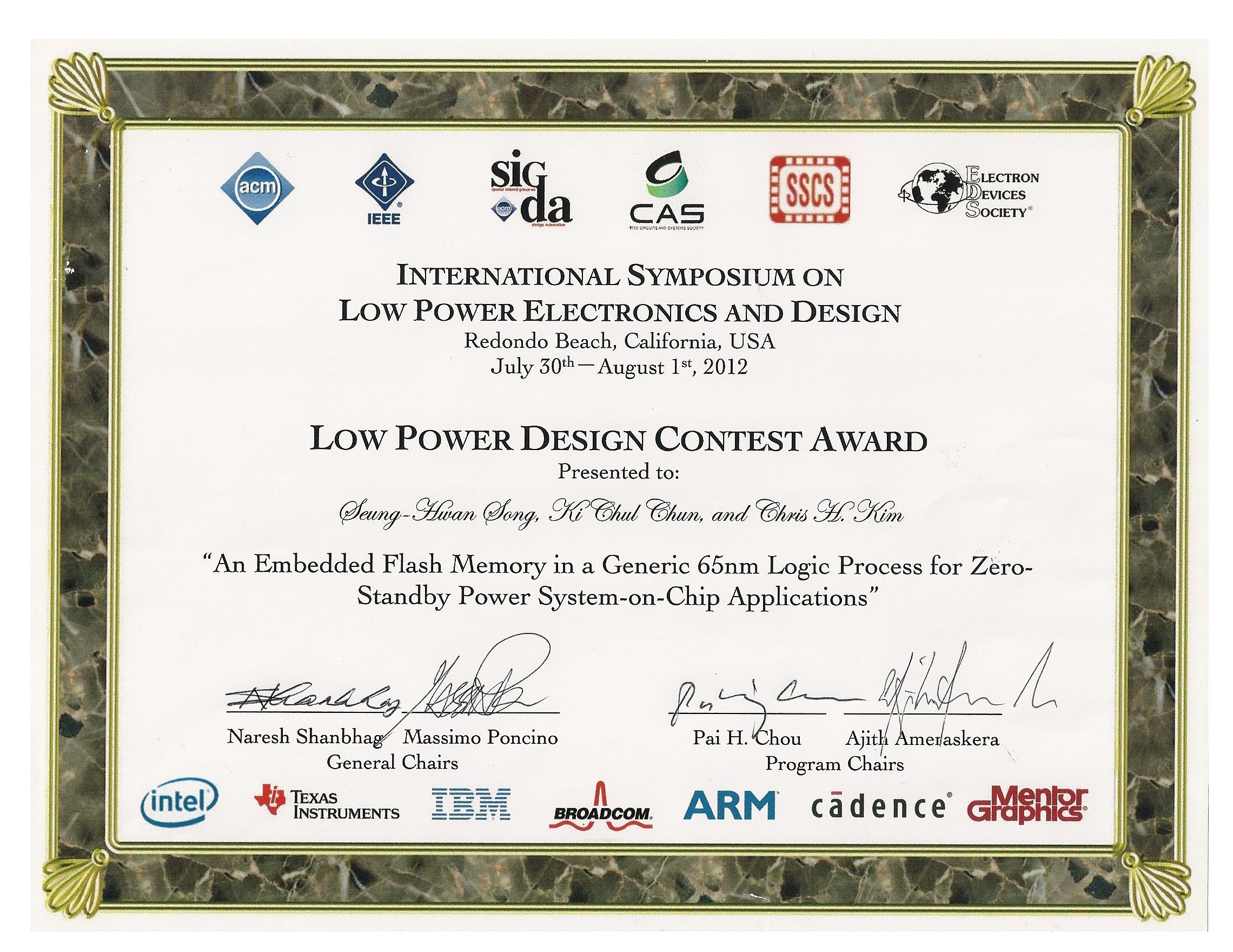

Based on the award winning technology from IEEE ISLPED low power design contest, our Logic EFlash has been oriented from the base research at University of Minnesota since 2009 and featured in 10+ IEEE VLSI, CICC, IEDM, IRPS, JSSC, TED papers so far. Our unique cell erase and program operations deploy reliable FN tunneling mechanisms with proprietary array architecture and reliable over-stress free high voltage circuits.

Standard Logic Based Non-Volatile Memory Cell

Cell Erase and Program Operations Using a FN Tunneling Mechanism

Award

References

M. Kim, M. Liu, L. Everson, and C.H. Kim, “An Embedded NAND Flash-Based Compute-In-Memory Array Demonstrated in a Standard Logic Process”, IEEE Journal of Solid-State Circuits (JSSC), Feb. 2022. [link]

M. Kim, J. Song and C.H. Kim, “Reliability Characterization of Logic-Compatible NAND Flash Memory based Synapses with 3-bit per Cell Weights and 1uA Current Steps”, International Reliability Physics Symposium (IRPS), Mar. 2020. [link]

M. Kim, M. Liu, L. Everson, G. Park, Y. Jeon, S. Kim, S. Lee, S. Song, and C.H. Kim, “A 3D NAND Flash Ready 8-Bit Convolutional Neural Network Core Demonstrated in a Standard Logic Process”, IEEE International Electron Devices Meeting (IEDM), pp. 38.3.1-4, Dec. 2019. [link]

M. Liu and C.H. Kim, “A Powerless and Non-volatile Counterfeit IC Detection Sensor in Standard Logic Processes Based on an Exposed Floating-Gate Array”, IEEE Trans. on Electron Devices (TED), Issue 6, Vol. 66, pp. 2735-2740, June 2019. [link]

M. Kim, J. Kim, C. Park, L. Everson, H. Kim, S. Song, S. Lee, and C. H. Kim, “A 68 parallel row access neuromorphic core with 22k multi-level synapse based on logic-compatible embedded flash memory technology,” 2008 IEEE International Electron Devices Meeting (IEDM), pp. 15.4.1-4, Dec. 2018. [link]

M. Liu and C.H. Kim, “A Powerless and Non-volatile Counterfeit IC Detection Sensor in a Standard Logic Process Based on an Exposed Floating-Gate Array”, VLSI Technology Symposium, June 2017 [link]

Seung-Hwan Song, Jongyeon Kim, and Chris H. Kim, “Overstress-Free 4×VDD Switch in a Generic Logic Process Supporting High and Low Voltage Modes,” IEIE Journal of Semiconductor Technology and Science (JSTS), Vol. 15, No. 6, pp. 664-670, Dec. 2015. [link]

Seung-Hwan Song, Jongyeon Kim, and Chris H. Kim, “A Comparative Study of Single-Poly Embedded Flash Memory Disturbance, Program/Erase Speed, Endurance, and Retention Characteristic,” IEEE Transactions on Electron Devices (TED), Vol. 61, No. 11, pp. 3737-3743, Nov. 2014. [link]

Seung-Hwan Song, Ki Chul Chun, and Chris H. Kim, “A Bit-by-Bit Re-Writable Eflash in a Generic 65 nm Logic Process for Moderate-Density Non-Volatile Memory Applications,” IEEE Journal of Solid-State Circuits (JSSC), Vol. 49, No. 8, pp. 1861-1871, Aug. 2014. [link]

Seung-Hwan Song, Ki Chul Chun, and Chris H. Kim, “A Logic-Compatible Embedded Flash Memory for Zero-Standby Power System-on-Chips Featuring a Multi-Story High Voltage Switch and a Selective Refresh Scheme,” IEEE Journal of Solid-State Circuits (JSSC), Vol. 48, No. 5, pp. 1302-1314, May 2013. [link]

Seung-Hwan Song, Ki Chul Chun, and Chris H. Kim, “A Bit-by-Bit Re-Writable Eflash in a Generic Logic Process for Moderate-Density Embedded Non-Volatile Memory Applications,” IEEE Custom Integrated Circuits Conference (CICC), pp. 1-4, Sep. 2013. [link]

Seung-Hwan Song, Jongyeon Kim, and Chris H. Kim, “Program/Erase Speed, Endurance, Retention, and Disturbance Characteristics of Single-Poly Embedded Flash Cells,” IEEE International Reliability Physics Symposium (IRPS), pp. MY.4.1-6, Apr. 2013. [link]

Seung-Hwan Song, Ki Chul Chun, and Chris H. Kim, “A Logic-Compatible Embedded Flash Memory Featuring a Multi-Story High Voltage Switch and a Selective Refresh Scheme,” IEEE Symposium on VLSI Circuits (VLSIC), pp. 130-131, Jun. 2012. [link]